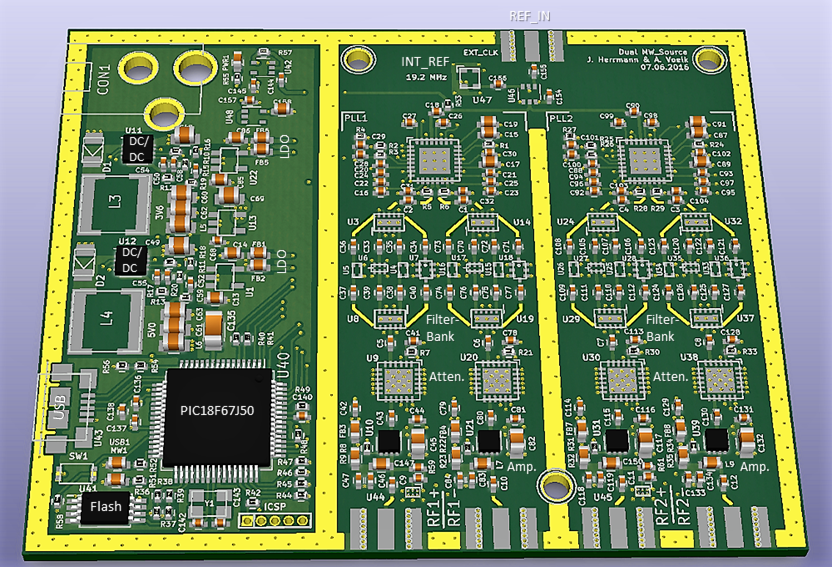

This new revisions builds up on the schematic resources of the Dual Source.

The biggest changes in this design, are a more powerful microcontroller and an input for an external clock signal,

The PIC18F67J50 with its high count of additional I/O pins replaces the old microcontroller with the GPIO expander.

Moreover, a new I2C external EEPROM allows the storage of user configuration and calibration data.

In order to allow an synchronization of the microwave signals an extra SMA input allows the user to feed in an external clock signal.

A subsequent RF-switch allows to switch between the on-baord Local Oscillator (19.2 MHz) and the external input (< 100 MHz).

Fig. 1. - Rendered 3D Model from KiCad.

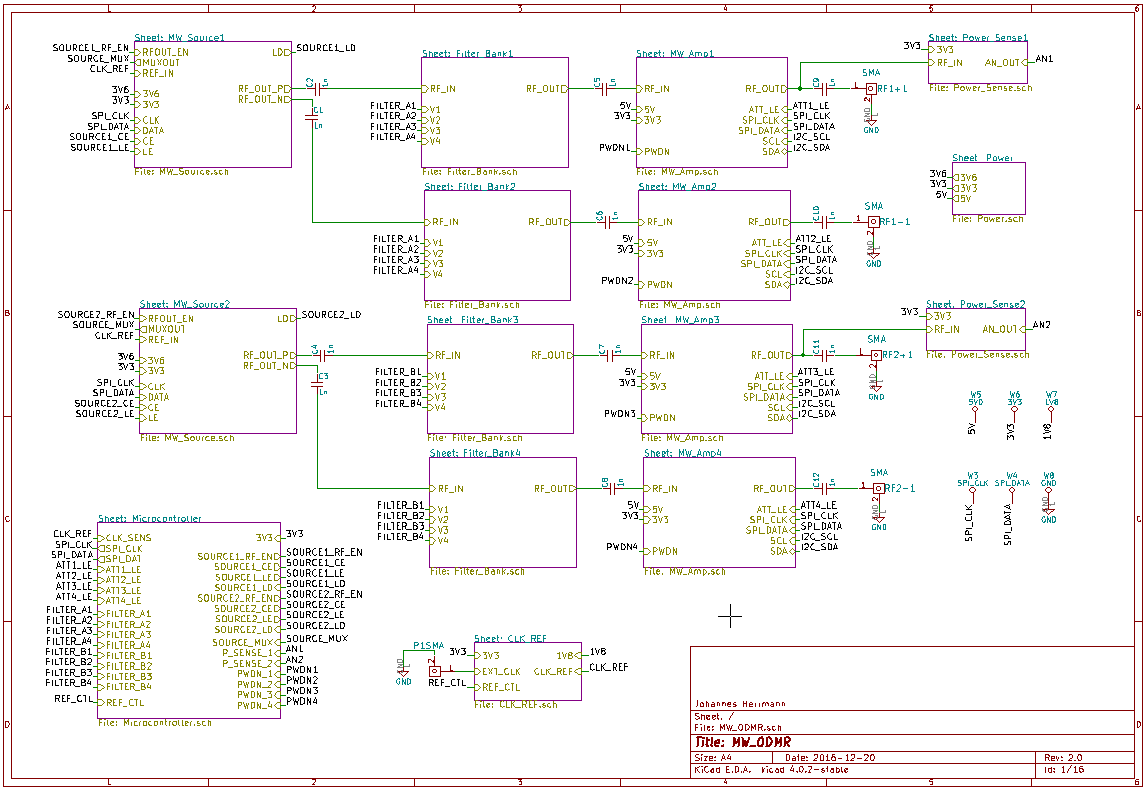

Schematic. Click for PDF.

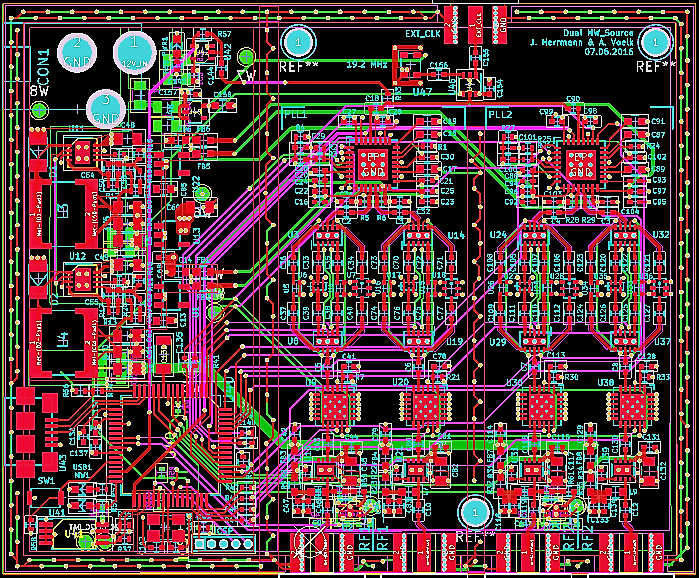

Layout Revision

The new layout includes more space for the RF-traces and an ground shielding around the PCB outline and the two PLLs.

Mounting holes for an aluminium case are also provided. Additionally, a 50 Ω matching at the output of the SMA connector for 6 GHz is attained by structuring

the underneath ground layer. The geometry of this plane has been verified by a field simulation with CST Microwave Studio®.

Fig. 2. - Board Layout from KiCad.

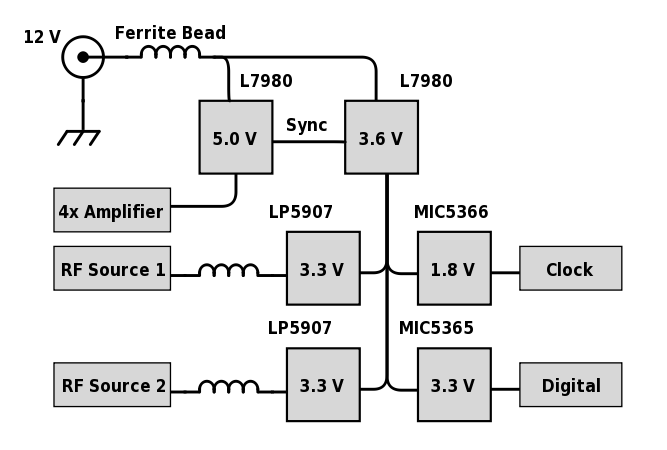

Power Supply Design

The basic power supply system is derived from the components of the

Single Source.

Here two synchronized step-down switching regulators create two basic voltage rails with 3.6 V and 5.0 V, respectively.

To assure a stable noise free supply for both PLLs two seperate ultra-low noise LDOs are used in combination with several ferrite beads.

The digital logic is supplied by a common 3.3 V switching regulator.

The internal reference clock for the PLL requires an input of 1.8 V which is supplied by a dedicated LDO.

Fig. 3. - Functional Diagram of the Power Supply Design.

New RF Power Detector Circuit

Except of the aforementioned changes, the old RF Power Detector Circuit has been replaced due to problems with its small BGA package and measurement gain.

The new Power Detector LTC5532 features a higher precision and controllable gain within a frequency range of 300 MHz to 7 GHz.

In order to measure the RF power at the output, an RF-splitter has to be designed.

Due to the wide bandwidth requirement, a resistive tap is the best choice here.

The coupling factor A of this structure can easily be calculated by using th internal impedance R of the detector IC:

A

The designed circuit aims for a coupling factor of 20dB, which is equivalent to R (here R).

The value of this coupling factor is highly depended on

the parasitics and accuracy of the chosen resistor and its geometry in the layout. Luckily the LTC5532 allows an adjustable

measurement gain. An additional output pin of this IC (V